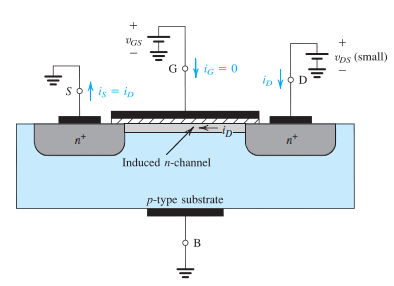

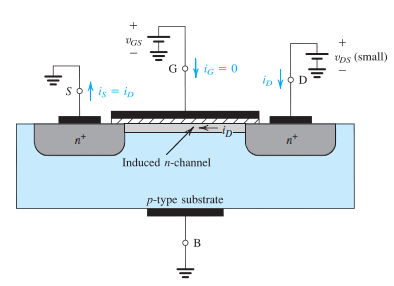

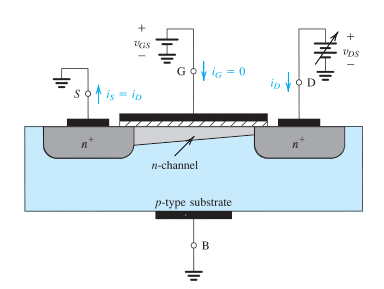

작은 VDS 전압을 인가할 때

VGS > Vt 일 때 채널의 전자들은 Drain으로 향하게 되고 전류(iD)는 전자의 흐름의 반대로 흐르게 됩니다.

이 때 전자의 속도는 이와 같습니다.

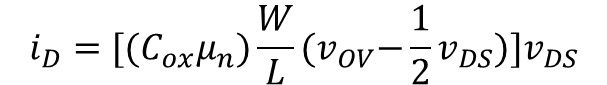

이때 iD의 식은 이렇게 표현할 수 있습니다.

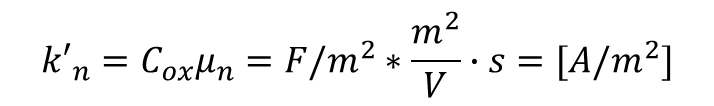

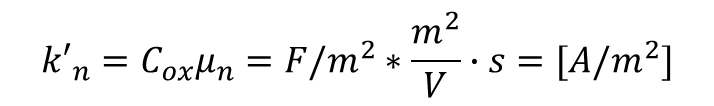

여기서 CoxUn 은 공정 트랜스컨덕턴스 파라미터 입니다.

이 공정 트랜스컨덕턴스 파라미터와 W/L의 곱은 MOSFET 트랜스컨덕턴스 파라미터로 표기됩니다.

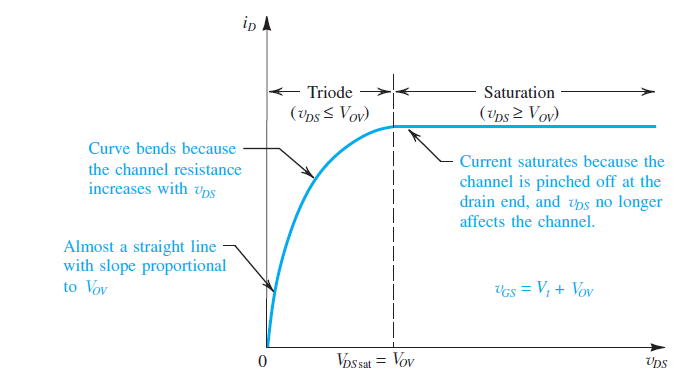

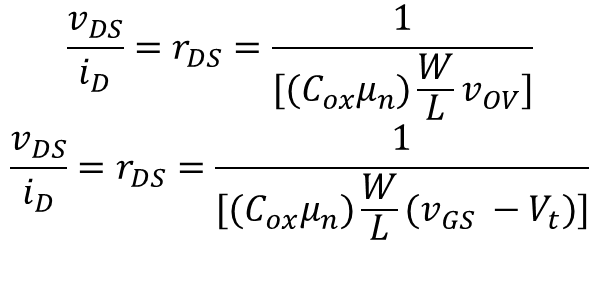

위 그래프를 보면 iD는 VGS에 의해 제어되는 선형 저항처럼 동작을 합니다.

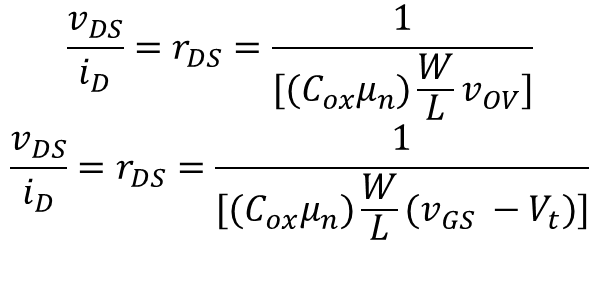

이 떄의 저항을 rDS로 표기하고 식은 아래와 같습니다.

rDS는 VGS<Vt 일 때 무한대이고 VGS가 Vt를 초과하면 그 값이 점점 감소합니다.

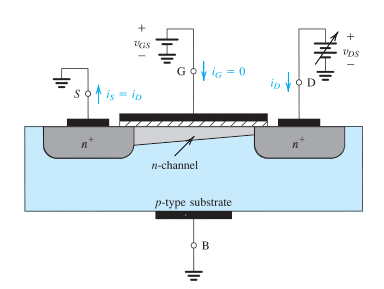

VDS 전압을 증가시킬 때

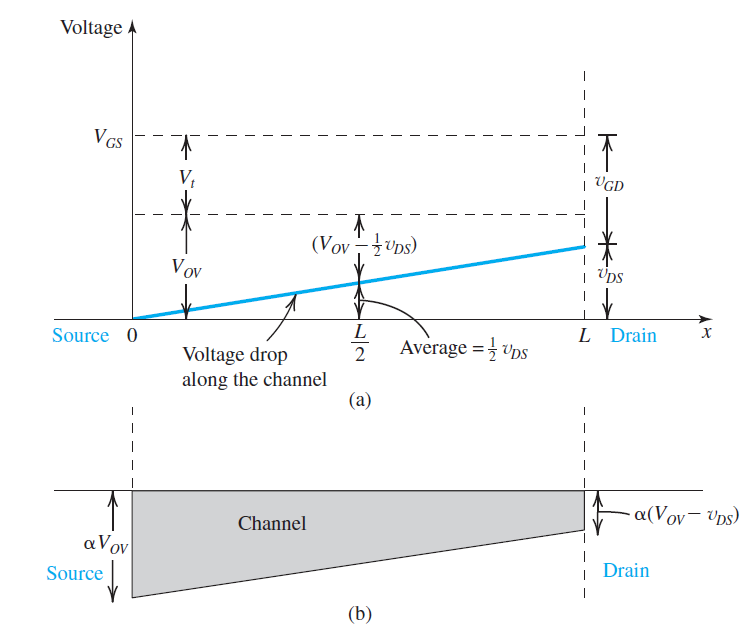

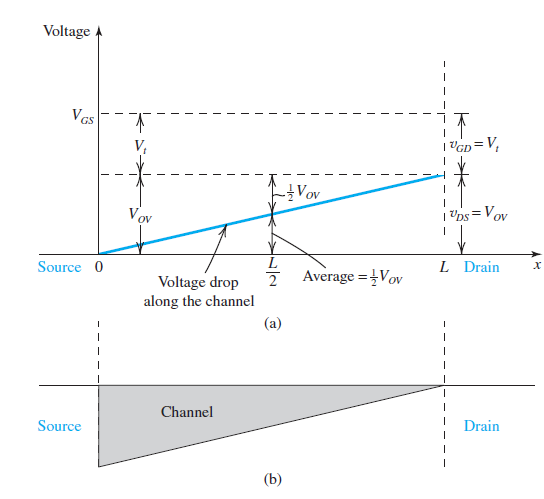

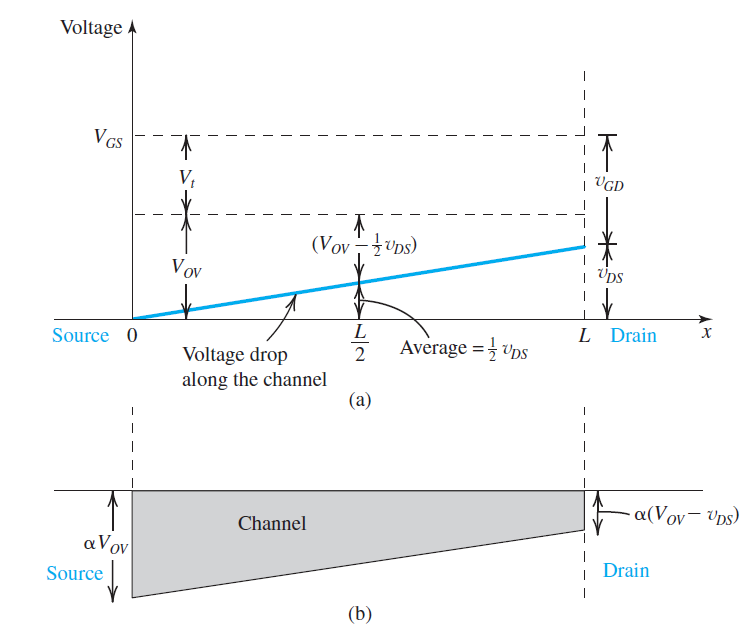

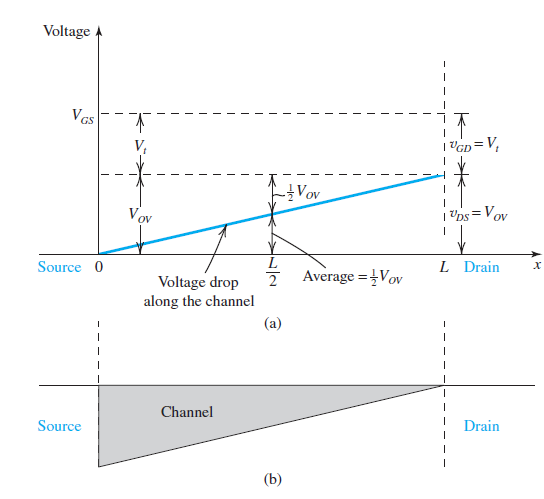

Gate에 전압 VGS > Vt를 기히고 VDS를 인가 했을 때 채널을 따라서 각 지점 사이의 전압이 달라집니다.

Soure -> Drain을 따라 갔을 때 0V --> VDS로 증가합니다.

그러므로 Gate를 기준으로 각 지점의 전압

Source의 끝 --> Drain의 끝 : VGS = Vt + Vov --> VGD = VGS - VDS = Vt + Vov - VDS 으로 감소하게 됩니다.

채널의 깊이는 전압에 의존하여 존재하므로 사실은 채널이 일정하지 않다는 것을 알 수 있습니다.(그림 2-1)

VDS가 증가하게 된다면 이 채널의 기울기는 더욱 경사질 것이고 이에 따라 채널 저항도 증가합니다.

채널의 전하는 채널의 단면적에 비례하므로 면적은 (Vov-0.5(VDS))에 비례합니다.

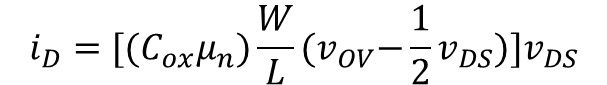

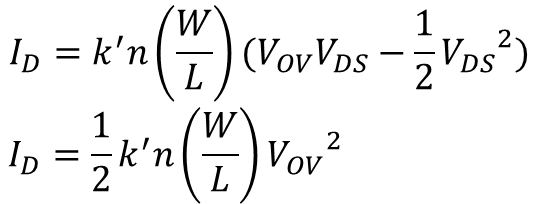

그러므로 iD와 VDS의 관계식에서 Vov를 (Vov-0.5(VDS))으로 바꾸면 아래와 같이 됩니다.

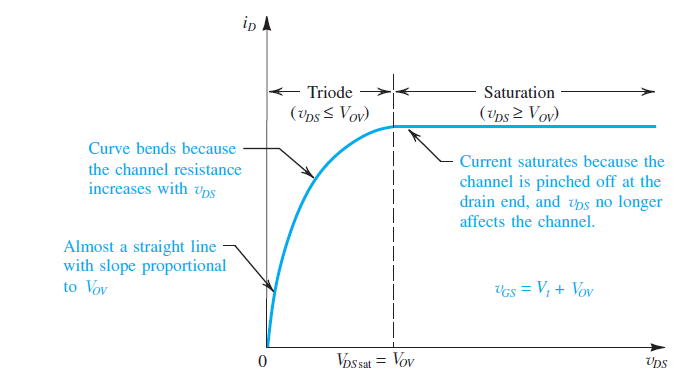

이 식을 통해 iD-VDS 특성 곡선은 아래와 같이 변하게 됩니다.

VDS가 매우 작은 값으면 위에서 1/2*VDS는 무시할 수 있습니다.

따라서 위에서 보았던 VDS가 작은 값일 때의 식과 동일해집니다.

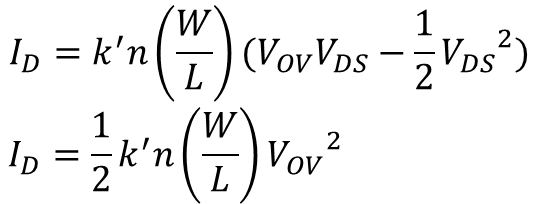

iD에 대한 식은 아래와 같이 3가지로 표현할 수 있습니다.

VDS >= Vov일 때 : 채널 핀치 오프와 전류 포화

이전까지의 경우 채널이 경사지긴 했어도 여전히 Drain 쪽에서 채널의 깊이는 0이 아닌 값이었다.

이번엔 VDS = Vov 일 때 VGD = Vt 이고 Drain 쪽의 채널 깊이가 0일 때를 보겠다.

아래의 수식을 보면 VDS = Vov일 때 왜 VGD = Vt 인지 이해 할 수 있다.

Drain의 채널 깊이가 인 것은 채널 핀치 오프(Channel pinch-off)를 야기한다.

이 때가 VDS = Vov 일 때이고 이 경우 VDS > Vov 가 되도록 VDS를 증가시켜도 채널의 모양과 전하에는 영향을 미치지 않고 그대로 유지한다.

따라서 Drain 전류의 식에서 VDS = Vov를 대입하여 포화 영역에서의 전류를 구할 수 있다.

이 때 MOSFET은 포화 영역(Saturation region)에 들어갔다고 할 수 있다.

이 때 VDS를 VDSsat으로 표현한다.

채널 핀치 오프는 채널 차단이아니다.

전류는 핀치 오프 채널을 통해 계속해서 흐르고 일정하게 유지한다.(iD-VDS 특성 곡선 참고)

따라서 MOSFET이 포화 영역(VDS >= Vov) 일 때의 Drian 전류를 아래와 같이 표현할 수 있다.

'이론 > 전자회로' 카테고리의 다른 글

| [MOSFET]전계 효과 트랜지스터-4(CLME) (0) | 2023.05.21 |

|---|---|

| [MOSFET]전계 효과 트랜지스터-3(NMOS VS PMOS) (0) | 2023.05.21 |

| [MOSFET] 전계 효과 트랜지스터-1(채널의 형성) (0) | 2023.05.13 |

작은 VDS 전압을 인가할 때

VGS > Vt 일 때 채널의 전자들은 Drain으로 향하게 되고 전류(iD)는 전자의 흐름의 반대로 흐르게 됩니다.

이 때 전자의 속도는 이와 같습니다.

이때 iD의 식은 이렇게 표현할 수 있습니다.

여기서 CoxUn 은 공정 트랜스컨덕턴스 파라미터 입니다.

이 공정 트랜스컨덕턴스 파라미터와 W/L의 곱은 MOSFET 트랜스컨덕턴스 파라미터로 표기됩니다.

위 그래프를 보면 iD는 VGS에 의해 제어되는 선형 저항처럼 동작을 합니다.

이 떄의 저항을 rDS로 표기하고 식은 아래와 같습니다.

rDS는 VGS<Vt 일 때 무한대이고 VGS가 Vt를 초과하면 그 값이 점점 감소합니다.

VDS 전압을 증가시킬 때

Gate에 전압 VGS > Vt를 기히고 VDS를 인가 했을 때 채널을 따라서 각 지점 사이의 전압이 달라집니다.

Soure -> Drain을 따라 갔을 때 0V --> VDS로 증가합니다.

그러므로 Gate를 기준으로 각 지점의 전압

Source의 끝 --> Drain의 끝 : VGS = Vt + Vov --> VGD = VGS - VDS = Vt + Vov - VDS 으로 감소하게 됩니다.

채널의 깊이는 전압에 의존하여 존재하므로 사실은 채널이 일정하지 않다는 것을 알 수 있습니다.(그림 2-1)

VDS가 증가하게 된다면 이 채널의 기울기는 더욱 경사질 것이고 이에 따라 채널 저항도 증가합니다.

채널의 전하는 채널의 단면적에 비례하므로 면적은 (Vov-0.5(VDS))에 비례합니다.

그러므로 iD와 VDS의 관계식에서 Vov를 (Vov-0.5(VDS))으로 바꾸면 아래와 같이 됩니다.

이 식을 통해 iD-VDS 특성 곡선은 아래와 같이 변하게 됩니다.

VDS가 매우 작은 값으면 위에서 1/2*VDS는 무시할 수 있습니다.

따라서 위에서 보았던 VDS가 작은 값일 때의 식과 동일해집니다.

iD에 대한 식은 아래와 같이 3가지로 표현할 수 있습니다.

VDS >= Vov일 때 : 채널 핀치 오프와 전류 포화

이전까지의 경우 채널이 경사지긴 했어도 여전히 Drain 쪽에서 채널의 깊이는 0이 아닌 값이었다.

이번엔 VDS = Vov 일 때 VGD = Vt 이고 Drain 쪽의 채널 깊이가 0일 때를 보겠다.

아래의 수식을 보면 VDS = Vov일 때 왜 VGD = Vt 인지 이해 할 수 있다.

Drain의 채널 깊이가 인 것은 채널 핀치 오프(Channel pinch-off)를 야기한다.

이 때가 VDS = Vov 일 때이고 이 경우 VDS > Vov 가 되도록 VDS를 증가시켜도 채널의 모양과 전하에는 영향을 미치지 않고 그대로 유지한다.

따라서 Drain 전류의 식에서 VDS = Vov를 대입하여 포화 영역에서의 전류를 구할 수 있다.

이 때 MOSFET은 포화 영역(Saturation region)에 들어갔다고 할 수 있다.

이 때 VDS를 VDSsat으로 표현한다.

채널 핀치 오프는 채널 차단이아니다.

전류는 핀치 오프 채널을 통해 계속해서 흐르고 일정하게 유지한다.(iD-VDS 특성 곡선 참고)

따라서 MOSFET이 포화 영역(VDS >= Vov) 일 때의 Drian 전류를 아래와 같이 표현할 수 있다.

'이론 > 전자회로' 카테고리의 다른 글

| [MOSFET]전계 효과 트랜지스터-4(CLME) (0) | 2023.05.21 |

|---|---|

| [MOSFET]전계 효과 트랜지스터-3(NMOS VS PMOS) (0) | 2023.05.21 |

| [MOSFET] 전계 효과 트랜지스터-1(채널의 형성) (0) | 2023.05.13 |