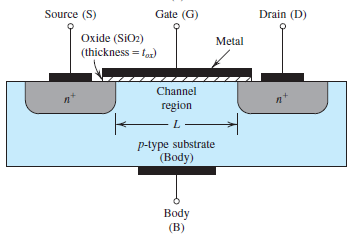

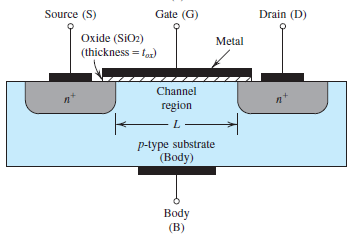

위 사진은 증가형 NMOS 트렌지스터의 물리적 구조 사진입니다.

MOS 앞 글자에 N 또는 P 가 들어가게 되는데 이는 Drain과 Source 단자가 n영역 기판으로 구성되어 있음을 의미합니다.

이 Drain과 Source는 Body라는 기판 위에 형성되는데 이 때 Body는 반대로 p영역 기판으로 구성됩니다.

Drain과 Source의 위쪽에는 이산화 실리콘층이 성장되어 있고 이 층은 Drain과 Source 영역 사이를 일부 덮고 있습니다.

이 부분을 Gate 단자라고 합니다.

Gate 전압이 0V 일 때

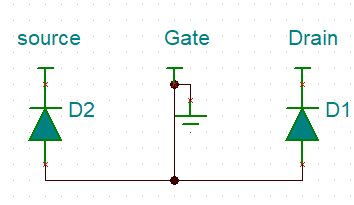

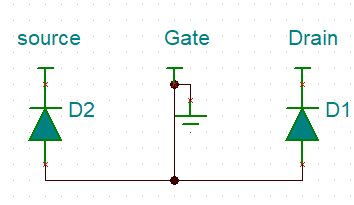

Gate의 전압이 0V 일 때는 Drain과 Source 사이에 애노드 단자를 맞댄 다이오드가 생깁니다.

위 사진을 보시면 이해가 되실 겁니다. 따라서 VDS(Drain과 Source 사이의 전압)이 인가되었을 때

다이오드로 인해 전류가 흐르는 것을 막게되고 매우 높은 저항을 가지게 됩니다.

Gate 전압에 VGS 전압을 인가할 때

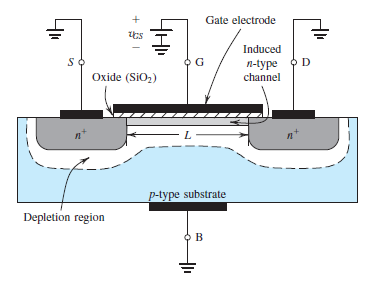

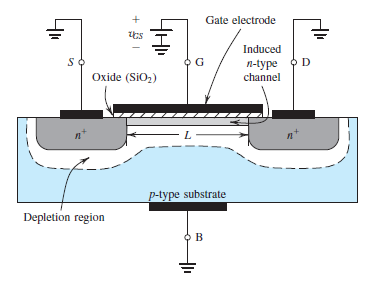

Drain과 Source 단자는 GND로 Gate 단자에는 VGS 전압을 인가한 사진입니다.

NMOS에서 Gate의 전압은 Source와 Gate 전압과 같으므로 VGS로 표기합니다.

Gate에 양의 전압을 인가하였으므로 Gate 바로 밑에 있던 정공들이 밑으로 밀려나게 되고

그 사이에는 공핍영역(Depletion region)이 생기게 됩니다.

이 공핍영역에는 억셉터 원자와 속박 음전하로만 채워져 있는데요.

이 음전하들은 본래 정공과 합쳐져 중화되었었지만 정공이 밀려나게 되면서 모습을 드러낸 것입니다.

그리고 양의 전압은 Drain과 Source에 있는 전자들을 끌어당기면서 n영역이 형성되게 됩니다.

이것이 바로 위 사진의 Induced n-type channel 입니다.

이 채널을 통해 Drain에서 Source로 전류가 흐를 수 있는 경로가 생기게 되었습니다.

이렇게 n채널이 형성되므로 n채널 MOSFET, NMOS 트렌지스터로 불립니다.

전자가 충분히 이동할 수 있을 만큼의 채널을 만들려면 VGS 전압을 높여야 하는데

이 기준 전압을 문턱전압(Vt : Threshold voltage)라고 합니다.

이 값은 제조 과정을 통해 조절됩니다.

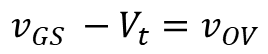

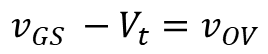

VGS가 Vt를 초과한 전압을 실효전압, 과구동전압(Vov : Override Voltage)라고 하며

식은 아래와 같습니다.

Gate와 채널 사이는 커패시터를 형성합니다.

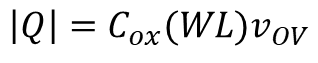

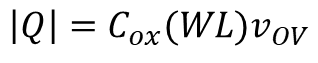

채널의 전하의 크기는 아래와 같고

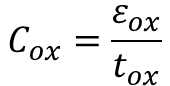

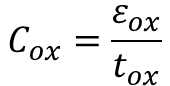

산화물 커패시턴스 Cox는 단위 게이트 면적당 평행판 커패시터의 커패시턴스 입니다.

W는 채널 폭, L은 채널의 길이입니다.

산화물 커패시턴스는 산화물의 유전율 / 산화물 두께로 알 수 있습니다.

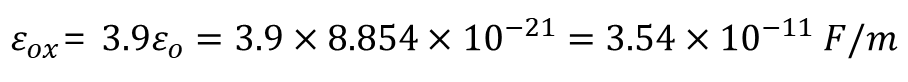

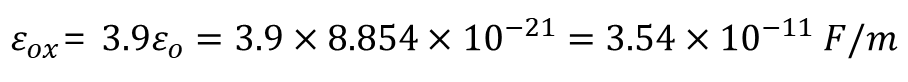

실리콘 산화물의 유전율

tox는 산화물 두께로 제조 공정 기술을 따라갑니다. 4nm 공정의 경우 tox는 4nm를 대입하면 됩니다.

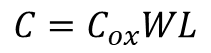

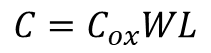

따라서 Gate와 채널 사이의 총 커패시턴스는 아래와 같습니다.

'이론 > 전자회로' 카테고리의 다른 글

| [MOSFET]전계 효과 트랜지스터-4(CLME) (0) | 2023.05.21 |

|---|---|

| [MOSFET]전계 효과 트랜지스터-3(NMOS VS PMOS) (0) | 2023.05.21 |

| [MOSFET]전계 효과 트랜지스터-2(VDS) (1) | 2023.05.13 |

위 사진은 증가형 NMOS 트렌지스터의 물리적 구조 사진입니다.

MOS 앞 글자에 N 또는 P 가 들어가게 되는데 이는 Drain과 Source 단자가 n영역 기판으로 구성되어 있음을 의미합니다.

이 Drain과 Source는 Body라는 기판 위에 형성되는데 이 때 Body는 반대로 p영역 기판으로 구성됩니다.

Drain과 Source의 위쪽에는 이산화 실리콘층이 성장되어 있고 이 층은 Drain과 Source 영역 사이를 일부 덮고 있습니다.

이 부분을 Gate 단자라고 합니다.

Gate 전압이 0V 일 때

Gate의 전압이 0V 일 때는 Drain과 Source 사이에 애노드 단자를 맞댄 다이오드가 생깁니다.

위 사진을 보시면 이해가 되실 겁니다. 따라서 VDS(Drain과 Source 사이의 전압)이 인가되었을 때

다이오드로 인해 전류가 흐르는 것을 막게되고 매우 높은 저항을 가지게 됩니다.

Gate 전압에 VGS 전압을 인가할 때

Drain과 Source 단자는 GND로 Gate 단자에는 VGS 전압을 인가한 사진입니다.

NMOS에서 Gate의 전압은 Source와 Gate 전압과 같으므로 VGS로 표기합니다.

Gate에 양의 전압을 인가하였으므로 Gate 바로 밑에 있던 정공들이 밑으로 밀려나게 되고

그 사이에는 공핍영역(Depletion region)이 생기게 됩니다.

이 공핍영역에는 억셉터 원자와 속박 음전하로만 채워져 있는데요.

이 음전하들은 본래 정공과 합쳐져 중화되었었지만 정공이 밀려나게 되면서 모습을 드러낸 것입니다.

그리고 양의 전압은 Drain과 Source에 있는 전자들을 끌어당기면서 n영역이 형성되게 됩니다.

이것이 바로 위 사진의 Induced n-type channel 입니다.

이 채널을 통해 Drain에서 Source로 전류가 흐를 수 있는 경로가 생기게 되었습니다.

이렇게 n채널이 형성되므로 n채널 MOSFET, NMOS 트렌지스터로 불립니다.

전자가 충분히 이동할 수 있을 만큼의 채널을 만들려면 VGS 전압을 높여야 하는데

이 기준 전압을 문턱전압(Vt : Threshold voltage)라고 합니다.

이 값은 제조 과정을 통해 조절됩니다.

VGS가 Vt를 초과한 전압을 실효전압, 과구동전압(Vov : Override Voltage)라고 하며

식은 아래와 같습니다.

Gate와 채널 사이는 커패시터를 형성합니다.

채널의 전하의 크기는 아래와 같고

산화물 커패시턴스 Cox는 단위 게이트 면적당 평행판 커패시터의 커패시턴스 입니다.

W는 채널 폭, L은 채널의 길이입니다.

산화물 커패시턴스는 산화물의 유전율 / 산화물 두께로 알 수 있습니다.

실리콘 산화물의 유전율

tox는 산화물 두께로 제조 공정 기술을 따라갑니다. 4nm 공정의 경우 tox는 4nm를 대입하면 됩니다.

따라서 Gate와 채널 사이의 총 커패시턴스는 아래와 같습니다.

'이론 > 전자회로' 카테고리의 다른 글

| [MOSFET]전계 효과 트랜지스터-4(CLME) (0) | 2023.05.21 |

|---|---|

| [MOSFET]전계 효과 트랜지스터-3(NMOS VS PMOS) (0) | 2023.05.21 |

| [MOSFET]전계 효과 트랜지스터-2(VDS) (1) | 2023.05.13 |